# A Schmitt Trigger by means of Complimentary Pass Transistor Logic

Pullela Sai Tejaswi Department of Electronics & Communication Engineering Vignan University Vadlamudi, Guntur, India

Abstract— The current paper presents a Schmitt trigger circuit based on Complementary Pass Transistor Logic (CPTL). The hysteresis curves of proposed Schmitt trigger is presented, hysteresis width depends on supply voltage and transistor geometry. The performance of the proposed circuit is examined using Cadence and the model parameters of gpdk-180 nm CMOS process. Simulation results are presented. The Schmitt trigger layout is presented with optimized sizing and spacing in compliance to the design rules of gpdk-180 nm CMOS process.

# I. INTRODUCTION

The Schmitt trigger is a circuit used extensively in both the analog and digital circuits. The Schmitt trigger is a comparator circuit that incorporates positive feedback. When the input is higher than a certain chosen threshold, the output is high; when the input is lower than the other chosen threshold, the output is low and when the input is mediating the two, the output retains its value. The trigger is so designated because the output retains its value until the input changes sufficiently to trigger a change [1-6]. Several methods have been proposed to implement Schmitt trigger. However sizing up the Schmitt triggers (to rise and fall times of signals) increases layout area and power dissipation. It is well known that CMOS Schmitt triggers are the circuits that convert a varying voltage in to a stable logical signal [7-10]. They have been used extensively to improve on/off control and reduce the sensitivity to noise or disturbances. If noise magnitude of the input signal is less than switching threshold difference, Schmitt trigger will not respond, thus making the later immune to undesired noise. Schmitt trigger circuit has been widely used in the input buffers to increase noise immunity. Several Schmitt trigger circuits had been reported for different applications [11-25].

In this paper, we present a Schmitt trigger circuit based on complementary pass transistor logic. The remaining sections of the paper are structured as follows. The proposed circuit description is presented in section II. Simulation results are included in section III. Finally, conclusions are included in section IV.

# II. CIRCUIT DESCRIPTION

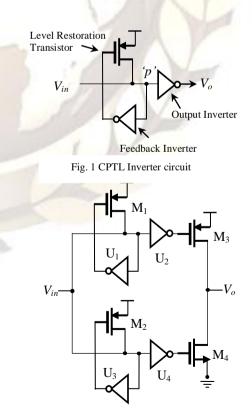

Figure 1 depicts the schematic diagram of CPTL inverter circuit. The CPTL uses series transistors to select between possible inverted output values of the logic, the output of which drives an Avireni Srinivasulu, Member, IEEE Department of Electronics & Communication Engineering Vignan University Vadlamudi, Guntur, India

inverter to generate the non-inverted output signal. Inverted and non-inverted inputs are needed to drive the gates of the pass-transistors. The main advantages are full swing, elimination of static power in the inverter through level restorer and pass transistor. Since restorer is only active when the input V<sub>i</sub> is high. The level restoration transistor improves capacitance; takes away pull down current at point 'p' strife between level restoration transistor and input transistor (slower switching). Hence level restoration transistor is also to be sized to its minimum level. Feedback inverter and level restoration transistor are also to be sized such that the voltage at node 'p' drops below the threshold of the inverter, which carries function in the sizes of output inverter.

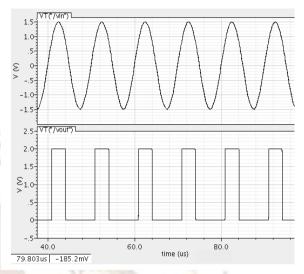

The new proposed Schmitt trigger is shown in Fig 2. It is comprised of two Complementary Pass Transistor Logic (CPTL) Inverters (CPTL<sub>1</sub> consists of  $M_1$ - $U_1$ - $U_2$ ) and (CPTL<sub>2</sub> consists of  $M_2$ - $U_3$ - $U_4$ ) and two output MOS transistors ( $M_3$  -  $M_4$ ).

Fig. 2 New proposed Schmitt trigger circuit

When no input signal is given, outputs of CPTL<sub>1</sub> and CPTL<sub>2</sub> are ON thereby M<sub>3</sub> is OFF and M<sub>4</sub> is ON. And the resultant output voltage is  $V_{out} = 0$  V. It is assumed that, input Vin is positive rising triangular waveform. When the input voltage  $V_{in}$  is greater than threshold voltage V<sub>th</sub>, outputs of CPTL<sub>1</sub> and CPTL<sub>2</sub> are OFF and thus  $M_3$  is ON and  $M_4$  is OFF hence  $V_{out}$  is positive (i.e., supply rail voltage 2 V). This point is called UTP. The output voltage Vout remains positive until the input waveform reaches a value of less than  $V_{th}$  when input voltage  $V_{in}$  is less than  $V_{th}$ , the outputs of CPTL<sub>1</sub> and CPTL<sub>2</sub> are ON thereby M<sub>3</sub> is OFF and  $M_4$  is ON and hence  $V_{out}=0$  V. This point is called LTP. The output voltage Vout remains zero until the input waveform voltage reaches a value of voltage greater than V<sub>th</sub>. The cycle repeats and generates a square waveform as shown in the figure 3.

Fig. 3. Input/output waveforms of the proposed trigger circuit

### **III. SIMULATION RESULTS**

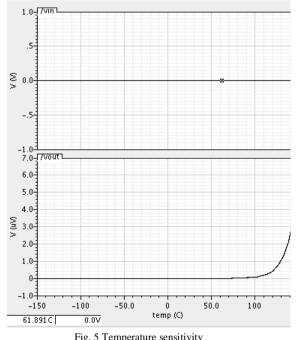

The proposed circuit is designed and analyzed using Cadence gpdk 180 nm CMOS technology. The new proposed CPTL based Schmitt trigger shown in Fig. 2 is simulated and its input and output results are shown in Fig. 4.

The proposed Schmitt trigger circuit with high to low and low to high transition threshold voltages has better noise immunity than the inverter. As input signal  $V_{in}$  goes up to  $V_{DD}$  from GND, the threshold voltages of the proposed Schmitt trigger circuit is  $V_H$ . Similarly as input signal  $V_{in}$  comes down to GND from  $V_{DD}$ , the threshold voltages of the proposed Schmitt trigger circuit is  $V_L$ . In other words, output signal  $V_o$  is pulled up as signal  $V_{in}$  is lower than  $V_L$ . Hence the noise immunity of the proposed Schmitt trigger circuit is better than that of inverter.

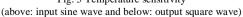

The circuit in Fig. 2 was tested for temperature stability ranging from  $-150^{\circ}$ C to  $+150^{\circ}$ C and the simulation profile produced to be less than 0.0003% variation in the case of square waveform. Figure 5

presents the temperature sensitivity of the proposed configuration. Simulated total power dissipation of the circuit is 28 pW.

Fig. 4 Input and output waveforms of the Schmitt Trigger

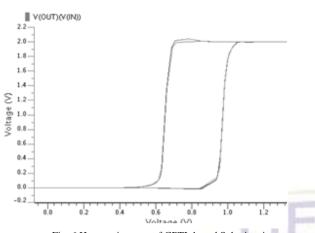

Hysteresis curve shown in Fig. 6 is plotted using TSMC 180 nm CMOS technology process with 2 V supply voltage.

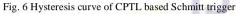

The Schmitt trigger layout is laid out with optimized sizing and spacing in compliance to the design rules of gpdk-180 nm CMOS process. The values of length and width and overall area of the proposed circuits are listed in table 1 and designed layout is shown in Fig. 7. The overall area occupied by the Complementary Pass Transistor Logic (CPTL) based Schmitt trigger is 148.58 µm<sup>2</sup>.

Fig. 7 Layout of the proposed CPTL based Schmitt trigger circuit

#### IV. CONCLUSION

A new CPTL based Schmitt trigger circuit, which has been realized using 180 nm CMOS technology is proposed and its characteristics have been quantified both analytically and numerically. The hysteresis feature is clear and less sensitive to the process and supply voltage variations compared to other CMOS Schmitt trigger. The new proposed Schmitt trigger circuit is suitable to reject noise for mixed voltage interface applications. The Schmitt trigger circuit described in this paper can be used as basic circuit for making more complex logic circuits with hysteresis transfer characteristics. The circuit may gain greater importance as it is bestowed with wider applications in many electronics and communication systems.

#### REFERENCES

- O. H. Schmitt, "A thermionic trigger," *Journal of Scientific Instruments*, vol. 15, pp. 24.26, Jan. 1938.

- [2] Di Cataldo, G., Palumbo, G., "New CMOS current schmitt triggers", in proc. of the IEEE International Symposium on Circuits and Systems (ISCAS), vol. 3, pp. 1292-1295, 1992.

- [3] Avireni Srinivasulu., "A novel current conveyor based Schmitt trigger and its application as a relaxation oscillator," *International Journal of Circuit Theory and Applications* (Wiley Inter-Science), vol. 39, no. 6, pp. 679-686, 2011.

- [4] Wang, W. Guggenbuhl, "Novel CMOS current schmitt trigger" *Electronics Letters*, vol. 24, no. 24, pp. 1514-1516, Nov 1988.

- [5] Wang, W. Guggenbuhl, "CMOS Current Schmitt Trigger with Fully Adjustable Hysteresis," *Electronics Letters*, vol.25, no. 6, pp. 397-398, Mar 1989.

- [6] Cong-Kha Pham, "CMOS Schmitt Trigger Circuit with Controllable Hysteresis Using Logical Threshold Voltage Control Circuit," 6th IEEE/ACIS International Conference on Computer and Information Science (ICIS 2007), 2007.

- [7] Pratchayaporn Singhanath, Varakorn Kasemsuwan and Kittipol Chitsakul, "DTMOS Schmitt Ttrigger with fully adjustable hysteresis," 2011 International Conference on Circuits, System and Simulation, IPCSIT, vol. 7, pp. 165-170, 2011.

- [8] Singhanath, P., Suadet, A., Kanjanop, A., Thongleam, T., Kuankid, S., Kasemsuwan, V., "Low voltage adjustable CMOS Schmitt trigger", in proc. of the IEEE International Conference on Modeling, Simulation and Applied Optimization (ICMSAO), pp. 1-4, 2011.

- [9] Nagaraj, K., Satyam, M., "Novel CMOS Schmitt trigger", *IEE Electronic Letters*, vol.17, issue. 19, pp. 693-694, 1981.

- [10] B.L. Dokic, "CMOS Schmitt triggers", in proc. of the IEEE Electronic Circuits and Systems, vol. 131, issue. 5, pp. 197-202, 1984.

- [11] C. Zhang, A. Srivastava and P. K. Ajmera, "Low voltage CMOS Schmitt trigger circuits" *Electronics Letters*, vol. 39, no. 24, DOI: 10.1049/el:20031131.

- [12] Shih-Lun Chen, Ming-Dou Ker, "A new Schmitt trigger circuit in a 0.13μm 1/ 2.5V CMOS process to receive 3.3V input signals", in proc. of the IEEE International Symposium on Circuits and Systems (ISCAS), pp. 573-576, 2004.

- [13] Steyaert, M., Sansen, W., "Novel CMOS Schmitt trigger", *IEE Electronic Letters*, vol. 22, issue. 4, pp. 203-204, 1986.

- [14] Pfister, A., "Novel CMOS Schmitt trigger with controllable hysteresis", *IEE Electronic Letters*, vol. 28, issue. 7, pp. 639-641, 1992.

- [15] Wang, C.-S., Yuan, S.-Y.; Kuo, S.-Y., "Full-Swing BiCMOS Schmitt Trigger", in proc. of the IEE Circuits, Devices and Systems, vol.144, issue. 5, pp. 303-308, 1997.

- [16] Al-Sarawi, S.F., "Low power Schmitt trigger circuit", IEE Electronic Letters, vol. 38, issue. 18, pp. 1009-1010, 2002.

- [17] Cakici, T., Bansal, A., Roy, K., "A Low power four transistor Schmitt trigger for asymmetric double gate fully depleted SOI devices", *in proc. of the IEEE International SOI Conference*, pp. 21-22, 2003.

- [18] Zhang, C., Srivastava, A., Ajmera, P.K., "Low voltage CMOS Schmitt trigger circuits", *IEE Electronic Letters*, vol.39, issue. 24, pp. 1696-1698, 2003.

- [19] Pedroni, V.A., "Low-voltage high-speed Schmitt trigger and compact window comparator", *IEE Electronic Letters*, vol. 41, issue. 22, pp. 1213-1214, 2005.

[20] Katyal, V., Geiger, R.L., Chen, D.J., "Adjustable hysteresis

- [20] Katyal, V., Geiger, R.L., Chen, D.J., "Adjustable hysteresis CMOS Schmitt triggers", in proc. of the IEEE International Symposium on Circuits and Systems (ISCAS), pp. 1938-1941, 2008.

- [21] Zhige Zou, Xuecheng Zou, Dingbin Liao, Fan Guo, Jianming Lei, Xiaofei Chen, "A novel Schmitt trigger with low temperature coefficient", in proc. of the IEEE Asia Pacific Conference on Circuits and Systems (APCCAS), pp. 1398-1401, 2008.

- [22] F. Yuan, "A high-speed differential CMOS Schmitt trigger with regenerative current feedback and adjustable hysteresis", *Analog Integrated Circuit and Signal Processing*, vol. 63, no. 1, pp. 121-127, 2010.

- [23] F. Yuan, "Differential CMOS Schmitt trigger with tunable hysteresis", *Analog Integrated Circuit and Signal Processing*, vol. 62, No. 2, pp. 245-248, 2010.

- [24] A.S. Sedra and K. C. Smith, *Microelectronic Circuits*, Oxford University Press, 4th ed., 1998.

- [25] D. Pal, Avireni Srinivasulu, B. B. Pal, A. Demosthenous, and B. N. Das, "Current conveyor based square/triangular – waveform generators with improved linearity," *IEEE Transactions on Instrumentation and Measurement*, vol. 58, no. 7, pp. 2174-2180, Jul. 2009.